HDLBits答案(8)_Verilog半加器、全加器和行波进位加法器原理与设计

半加器、全加器和行波进位加法器原理与设计

半加器

基础知识介绍

在数字电路设计中,加法器是最基础的算术运算单元。理解加法器的工作原理,是我们学习数字系统的第一步。

什么是半加器?

半加器(Half Adder)是一种最基本的加法电路,它用于计算2个单比特二进制数的和。想象一下,这就像我们在小学时学的个位数加法,只不过这里只有0和1两个数字。

让我们用生活中的例子来类比:假设你有两个开关,每个开关要么打开(1)要么关闭(0)。半加器的工作就是告诉你:如果这两个开关代表的数字相加,结果是多少?

核心概念定义:

- 输入:两个单比特二进制数

a和b(取值只能是0或1) - 输出:

sum(简记为s):两个数的和(不考虑进位时的结果)carry(简记为c):进位输出(当两个数相加结果超过1时产生)

为什么叫”半”加器?

因为它只能处理两个输入位的相加,没有考虑来自低位的进位输入。在实际的多位加法运算中,每一位的计算都需要考虑前一位的进位,所以半加器只能完成”一半”的工作。

半加器的真值表:

| a | b | sum | carry |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

逻辑表达式:

sum = a XOR b(异或运算:相同为0,不同为1)carry = a AND b(与运算:只有都为1时结果才为1)

题目描述:实现一个半加器。半加器将两位比特相加(不带进位输入)并产生一个1bit结果和一个进位输出。

Solution:

1 | module top_module( |

全加器

基础知识介绍

理解了半加器后,我们来看全加器(Full Adder)。全加器才是实际数字系统中更常用的加法单元。

什么是全加器?

全加器在半加器的基础上,增加了一个进位输入 cin。这就意味着它可以同时处理:

- 当前位的两个输入

a和b - 来自低位的进位

cin

生活中的类比:

想象一下你在做多位数的加法,比如计算 123 + 456:

- 个位:3 + 6 = 9,没有进位

- 十位:2 + 5 = 7,也没有进位

- 百位:1 + 4 = 5

但如果是计算 189 + 234:

- 个位:9 + 4 = 13,写下3,进位1

- 十位:8 + 3 + 1(进位)= 12,写下2,进位1

- 百位:1 + 2 + 1(进位)= 4

在这个例子中,十位和百位的计算就用到了”全加器”的思想——不仅要加当前位的两个数,还要加上来自低位的进位!

核心概念定义:

- 输入:

a、b:两个单比特二进制数cin:来自低位的进位输入

- 输出:

sum:三个数的和(单比特结果)cout:进位输出(到高位的进位)

全加器的真值表:

| a | b | cin | sum | cout |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

题目描述:实现一个全加器。全加器将三位比特相加(带进位输入)并产生一个1bit结果和一个进位输出。

Solution:

1 | module top_module( |

行波进位加法器

基础知识介绍

现在我们已经掌握了1位全加器,如何用它来构建多位加法器呢?答案就是将多个全加器串联起来!

什么是行波进位加法器?

行波进位加法器(Ripple-carry adder,简称RCA)是一种最简单的多位加法器结构。它的工作原理是:将N个1位全加器依次级联,前一个全加器的进位输出作为后一个全加器的进位输入。

为什么叫”行波”进位?

因为进位信号是从最低位(LSB)向最高位(MSB)依次传递的,就像水波一样从起点向外扩散。每一位的计算都要等待前一位的进位结果出来后才能进行。

生活中的类比:

想象一条流水线的工人,每个人负责一个工位的工作。第一个工人完成自己的工作后,把半成品传给第二个工人;第二个工人完成后再传给第三个……以此类推。行波进位加法器的工作方式就是这样,每一位的计算都依赖于前一位的结果。

行波进位加法器的优缺点:

✅ 优点:结构简单,易于理解和实现

❌ 缺点:延迟较大,因为高位必须等待低位的进位信号

题目描述:现在我们已经知道如何实现一个全加器,我们将使用它的3个实例来创建一个3位二进制的行波进位加法器。

行波进位加法器将两个3位数字和一个进位相加以产生一个3位结果和一个进位输出。

Solution:

1 | module top_module( |

本节小结

行波进位加法器通过级联多个全加器来实现多位加法。虽然它结构简单,但由于进位信号需要逐位传递,在位数较多时会产生较大的延迟。在实际的高性能处理器中,通常会使用更复杂的加法器结构(如超前进位加法器)来减少延迟。

入门者避坑指南

在学习加法器设计的过程中,初学者很容易犯一些常见的错误。下面我们来总结几个最典型的问题,帮助大家少走弯路。

错误1:混淆拼接操作符的顺序

错误表现:1

2// ❌ 错误示例

assign {sum, cout} = a + b; // 顺序搞反了!

错误原因分析:

在Verilog中,位拼接操作符 {} 内的信号顺序是从左到右对应高位到低位。当我们计算两个1位数相加时,结果可能是2位(比如1+1=10),其中左边的1是进位(cout),右边的0是和(sum)。如果顺序搞反了,结果就完全错了!

正确做法对比:1

2// ✅ 正确示例

assign {cout, sum} = a + b; // cout是高位,sum是低位

调试技巧:

- 写测试时特别测试 a=1, b=1 的情况

- 如果sum得到1而cout得到0,说明顺序搞反了

错误2:忘记指定位宽导致隐式位宽扩展

错误表现:1

2// ❌ 错误示例

assign sum = a + b + 1; // 1没有指定位宽

错误原因分析:

在Verilog中,未指定位宽的常量会被默认视为32位(或更大),这可能导致意外的位宽扩展。虽然这个问题在加法器的简单例子中可能不会立即显现,但在复杂设计中会带来严重问题。

正确做法对比:1

2// ✅ 正确示例:明确指定位宽

assign {cout, sum} = a + b + 1'd0; // 1位的0

错误3:行波进位加法器中连接错误的进位信号

错误表现:1

2

3

4// ❌ 错误示例

assign {cout[0], sum[0]} = a[0] + b[0] + cin;

assign {cout[1], sum[1]} = a[1] + b[1] + cin; // 错误:还在使用cin!

assign {cout[2], sum[2]} = a[2] + b[2] + cin; // 错误:还在使用cin!

错误原因分析:

这是初学者最容易犯的错误之一!行波进位加法器的关键在于前一位的进位输出要连接到后一位的进位输入。如果每位都使用初始的cin,那每位之间就没有任何关联了,这就不叫”行波”进位了。

正确做法对比:1

2

3

4// ✅ 正确示例:进位信号依次传递

assign {cout[0], sum[0]} = a[0] + b[0] + cin;

assign {cout[1], sum[1]} = a[1] + b[1] + cout[0]; // 使用前一位的cout

assign {cout[2], sum[2]} = a[2] + b[2] + cout[1]; // 使用前一位的cout

调试技巧:

- 画一张简单的连线图,标清楚每个信号的流向

- 测试时使用会产生连续进位的数值(如全1加全1)

错误4:模块端口声明风格过时

错误表现:1

2

3

4

5

6// ❌ 错误示例:Verilog-1995风格,端口类型和数据方向分开声明

module top_module(a, b, cout, sum);

input a;

input b;

output cout;

output sum;

错误原因分析:

虽然这种旧的语法在某些仿真器中仍然可以工作,但它已经过时了。Verilog-2001引入的ANSI风格端口声明更加清晰、简洁,也更不容易出错。

正确做法对比:1

2

3

4

5

6

7// ✅ 正确示例:Verilog-2001 ANSI风格

module top_module(

input a,

input b,

output cout,

output sum

);

巩固练习

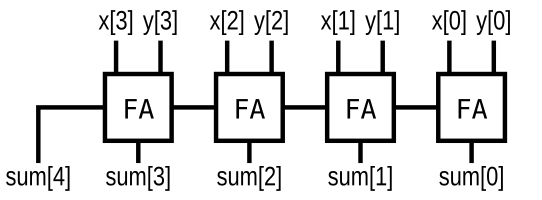

题目1:4位行波进位加法器

题目描述:实现下图所示电路,其中 “FA” 指全加器(Full Adder)。

Solution1:

1 | module top_module ( |

小贴士:

注意这个设计中,最终的进位输出变成了 sum[4],这是因为题目要求输出是一个5位的 sum 向量,其中包含了最终的进位。

题目2:有符号加法器的溢出检测

题目描述:

假设有两个8位数字的补码,a[7:0] 和 b[7:0]。这两个数字相加产生 s[7:0]。模块中需计算是否发生了(有符号的)溢出。

提示:当两个正数相加产生一个负结果,或两个负数相加产生一个正结果时,会发生符号溢出现象。有几种检测溢出的方法:可以通过比较输入和输出数字的符号来计算溢出,或者从最高位和次高位的进位来判断是否溢出。

Solution2:

1 | module top_module ( |

注意:

在补码表示中,最高位是符号位:0表示正数,1表示负数。只有当两个同号数相加时才可能发生溢出,异号数相加永远不会溢出!

题目3:100位加法器

题目描述:创建一个100位的二进制加法器。加法器将两个100位的数和一个进位相加产生一个100位的结果和一个进位。

Solution3:

1 | module top_module( |

小贴士:

对于位数很多的加法器,我们不需要手动去例化100个全加器!Verilog的综合器会自动为我们优化实现。这种写法既简洁又高效。

题目4:BCD行波进位加法器

题目描述:

已有一个BCD(二进制编码的十进制)数加法器,名为 bcd_fadd,它将两个BCD数字和进位信号相加,生成结果和进位信号。

1 | // 题目中给出的BCD加法器模块声明 |

实例化 bcd_fadd 的4个副本,以创建一个4位BCD行波进位加法器。

Solution4:

1 | module top_module( |

注意:

这个例子中我们使用了命名端口连接(.a(a[3:0]) 这种写法),这比位置连接更安全、更清晰,特别是在端口较多的模块实例化时。

总结

在这篇文章中,我们从最基础的半加器开始,逐步深入学习了:

- 半加器:处理两个1位数相加,没有进位输入

- 全加器:在半加器基础上增加了进位输入,可以处理三个1位数相加

- 行波进位加法器:通过级联多个全加器实现多位加法,进位信号从低位向高位”行波”传递

- 入门者避坑指南:总结了4个最常见的错误,帮助大家少走弯路

- 巩固练习:通过4个不同难度的练习题,加深对加法器的理解

从通信IC设计的角度来看,加法器是数字信号处理(DSP)中的核心单元之一。无论是滤波器、FFT变换还是调制解调,都离不开大量的加法运算。虽然行波进位加法器结构简单,但在高速通信系统中,我们往往需要使用更先进的加法器结构(如超前进位加法器、进位选择加法器等)来满足时序要求。

希望这篇文章能够帮助你打好加法器设计的基础!